咨询电话: 13704000378

半导体行业-光刻工艺(一)!

发布于 2025-12-05 16:43 阅读()

中将设计好的图形从光刻版或倍缩光刻版转印到晶圆表面的光刻胶上所使用的技术。光刻技术最先应用于印刷工业,并长期用于制造印刷电路板将定义在光刻胶上的图形转移到晶圆表面,晶圆表面上的光刻胶图形由光刻技术决定,因此光刻是集成电路生产中最重要的工艺技术。

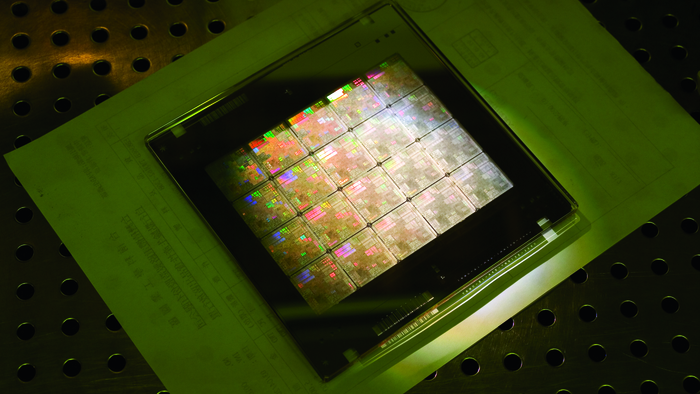

如下图所示,光刻技术是集成电路制造的核心。从裸片晶圆到键合垫片的刻蚀和去光刻胶为止,即使最简单的MOSIC芯片都需要5道光刻工艺,先进的集成电路芯片可能需要30道光刻工艺步骤。集成电路制造非常耗时,即使一天24小时无间断地工作,都需要6-8周时间才能将裸片晶圆制造成芯片晶圆,其中的光刻工艺技术就耗费了整个晶圆制造时间的40%-50%。

光刻技术的基本要求是高的分辨率、高的感光度、精确的对准及低的缺陷密度。IC制造技术的发展水平通过晶圆的最小图形尺寸衡量,2010年的最小图形尺寸为25nm(见下图)。最小图形尺寸越小,在一个晶圆上能制成的芯片也就越多。2010年的25nm技术受限于光刻技术的分辨率。通过提高分辨率,最小图形尺寸就能进一步缩小。光刻胶必须对曝光的光源十分敏感。光刻胶的感光度越高,曝光时间就越短,从而产量就越高。但如果感光度过高可能会对光刻胶的其他特性(包括分辨率)造成影响,因此必须在分辨率和感光度之间折中选择。先进的集成电路芯片需要30多道图形化过程,而且每一道工艺都必须和前一道工艺精确对准才能成功转移图形。由于对准时的最大误差范围是关键尺寸的10%-20%,所以只允许有极小的对准失误,对于25nm技术,对准失误必须控制在2.5-5.0nm的范围,所以先进的光刻技术需要有自动对准系统,每个工艺细节都必须准确控制,因此非常具有挑战性。比如,3mm晶圆上1℃的温差就会造成晶圆直径产生0.75um的尺寸差异,这是因为硅会以2.5×10e-6/℃的速率膨胀或收缩(温度更低时为收缩)。这个阶段产生的缺陷将经过后续的刻蚀或离子注入技术转移到元器件和电路上,进而影响产品的成品率和可靠性,因此光刻技术必须将缺陷密度降到最低。

光刻技术可以分为三个主要工艺流程:光刻胶涂敷、对准和曝光,以及光刻胶显影。首先在晶圆表面涂上一层感光薄膜,即所谓的光刻胶(PR),这层光刻胶经过光刻版或倍缩光刻版的紫外线曝光,光刻版上的明区或暗区通过绘图机根据集成电路设计而成。穿过明区的紫外线使曝光的光刻胶化学成分因光化学反应发生变化先进半导体生产中通常使用正光刻胶,曝光区会在显影剂里溶解,而未曝光的光刻胶则留在晶圆表面,这相当于复制了光刻版/倍缩光刻版的暗区图形。

新闻资讯

-

半导体行业-光刻工艺(一) 12-05

-

继豆包手机后字节AI眼镜也要来 12-05

-

艾森股份光刻胶等多款产品国产替 12-05

-

芯片光刻机是干什么用的 12-05

-

半导体国产替代提速!艾森股份“ 12-05

-

绕开EUV技术壁垒?中国光刻工 12-04

-

美国重振半导体雄心:15亿美元 12-04

-

Q3半导体设备市场中国大陆稳居 12-04